Времедиаграма RS- спусъка действие

Като независими продукти асинхронни RS-джапанки се използват като ключове, компилатор, дистрибуторите и така нататък. Н. Пулс оформянето чрез механични контакти.

Един пример RS- предизвика промишленото производство е 561TR2 IP.

В пакет IC съдържа четири идентични независим спусъка.

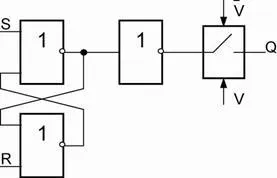

Логическа структура Условно изображение

Един чип спусъка

Изходът на инвертора служи като буфер между Т2 и сериен каскада.

V- общ позволи вход (контроли четирите клавиши). PRIV = "1" ключове за извършване на информация и PRIV = "0" няма информация за резултатите.

В някои серия RS-тригери като самостоятелни продукти на разположение.

Такива води лесно насрещни на конвенционални логически елементи. Освен това, в по-сложни праговите входове са страна Saira като предимство, което позволява по всяко време Tt настроен на "1" или "0", независимо от състоянието на други материали.

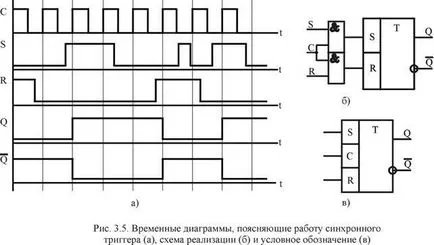

Синхронни тригери RS-

Синхронно (честота) тригери са получени от асинхронния RS- резето чрез свързване на входа на веригата за управление, състояща се от логически елементи.

Входове SiRinformatsionnye, влизането C - часовник (времето).

Когато С = 0, тригер съхранява информация SiRbezrazlichno държавни входове.

Смяна на спусъка състоянието на изхода е възможно само когато C = 1.

Пунктираните линии показват такива Sa IRA входа за монтаж единица спусъка асинхронен и нула състояние, заобикаляйки входовете за данни. В синхронна работа в синхронните входове трябва да поддържа неутрална комбинация.

Време превключвател закъснение се състои от синхронен тригер за разпространение на сигнала забавяне на входния елемент и превключване забавянето на собствената си тригер.

tzd.p. = TZD. стр. Ср + 2tzd. стр. ср = 3tzd. стр. Ср

Минималната продължителност на импулс, в случай на съвпадение на предния си информация сигнал може да бъде по-малко tzd.p. за забавяне във времето на логически вход елемент ()

Поради това, което позволява на Временната и честотна резолюция

Синхронни RS-тригер. За да се получи характеристика уравнението на синхронния RS-тригер състава на прехода маса, подобна на маса. 3, чрез въвеждане в него на трета променлива вход - синхронизиращия сигнал S. Когато С = 1 спусъка променя състоянието си в съответствие с логиката на асинхронни операцията на спусъка, и когато С = 0 флип-флоп посочено, остават непроменени.

От PDNF на прехода маса пишем характерното уравнение, което след минимизиране са на формата

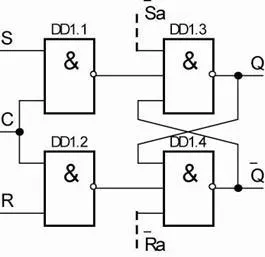

За конструиране на схемата на синхронен RS-тригер в основата на PE "И-НЕ" двойно proinvertiruem (8), ние получаваме в резултат на

Схемата, която изпълнява тези уравнения е показано на Фигура 8.

В основата на веригата е асинхронен

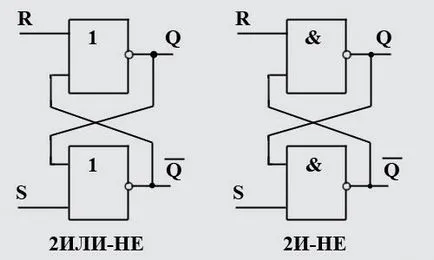

Функционалната диаграма показва RS-тригер асинхронен тип NAND и второто изпълнение на NOR елементи.

Как спусъка Trigger е проста цифрово устройство, което има способността за дълго време е в една от двете стабилни държави, т.е., в начина на съхранение на информация и под влияние на външни контролни сигнали рязко превключи на друг щат - запис на информация. Обикновено спусъка има два изхода - директен и обратен изход. Броят на записите, зависи от структурата и функцията на "спусъка". В момента на преход от едно състояние в друго се извършва възможно най-бързо, така че по време на преходни процеси могат да бъдат пренебрегвани в практиката. Тригери е основен логически елемент за изграждане на различни устройства за съхранение и схеми. Те лесно могат да се използват за съхраняване на информация, но размерът на паметта не е голям. Също така, той може да се съхранява на битовете отделни кодове или сигнали. Тези цифрови устройства са в състояние да се запази паметта си само ако захранващото напрежение. Поради това, на базата може да се дължи на основните схеми на RAM. Ако изключите токов кръг, а след това отново, спусъка ще бъде в напълно произволна състояние, тоест, неговата директен изход може да изглежда като логика нула и логическо ниво. Ето защо, осъзнавайки, проектиране на цифрови схеми, е необходимо да се вземе предвид моментът на спусъка в първоначалното състояние. В основата на всяка напълно определени спусъка верига, състояща се от две врати или И-ИЛИ-НЕ елемент, които са обхванати от положителната обратна връзка

4.2 тригери са действително по-сложни обекти, съставени от няколко (2-9) на прости логически врати. От това следва, че задейства модел може да бъде представен не само поведението, но и структурни модели, остава на същото ниво в йерархията, а именно на нивото на логика симулация (Фигура 1).

Фиг. 1. поведенчески и структурни модели затворен RS-тригер

Направен е опит да се създаде структурен модел за логика елемент неминуемо ще доведе до понижаване на нивото на йерархия в една стъпка, която е необходимо да се разглежда като елемент, тъй като системата формира от структурните примитивите на по-ниско ниво (транзистори, резистори, кондензатори и други компоненти). Следователно логиката моделиране е необходимо да се замени дизайн верига (електронен), придобиване в същото време всички недостатъци на прекалено много подробности.