Комбинирани цифрови устройства 1

Фиг. 15.8. логически елементи

Logic елемент следва да се прилага като отделна интегрална схема. Често интегралната схема съдържа множество логически елементи.

Логически елементи, използвани в цифрови електронни устройства (логически устройства) да извърши прости трансформация логически сигнали.

Класификация логически елементи. Има следните класове логически елементи (т.нар логика):

· Резистор-транзисторна логика (TRL);

· Диод-транзисторна логика (DTL);

· Транзистор-транзисторна логика (TTL);

· Емитер-транзисторна логика (ECL);

· Транзистор-транзисторна логика с Шотки диоди (STTL);

· Logic основава на MOS транзистори тип р канал (р -MDP);

· Логика на базата на транзистори MOS с канали тип п (п -MDP);

· Logic въз основа на допълнителни клавиши на транзистори MIS (CVR, CMOS);

· Интегрирана инжекция логика и 2 А;

· Логика базирани полупроводникови галиев арсенид GaAs.

Днес, най-широко използвани следната логика: TTL, STTL, CMOS, ECL. Логика порти и други цифрови електронни устройства се произвеждат като част от серия от чипове: TTL - K155, KM155, K133, KM133; STTL - 530, KR531, KM531, KR1531, 533, К555, Km555, 1533 KR1533; ECL - 100, K500, K1500; CMOS - 564, K561, 1564 KR1554; GaAs - K6500.

Най-важните параметри на логически елементи:

· Speed се характеризира със забавяне на разпространението време tzr сигнала и на максималната експлоатационна честота Fmax. Времето на забавяне обикновено се определя от разликите нива 0,5Uvh и 0.5 # 916; Vout. Максималната работна честота Fmax - ϶ᴛᴏ chastota͵ че запазва работоспособността верига.

· Load капацитет характеризиращ комбиниран коефициент ?? eniya въвеждане кочан (понякога се използва терминът ?? eniya''koeffitsient комбиниран с vyhodu ''). размер кочан - ϶ᴛᴏ брой на логическите входове, KRAZ стойност - максимален брой подобни логически елементи, които са свързани към изхода на логически елемент. Типичните стойности са в тях следва: кочан = 2 ... 8, KRAZ = 4 ... 10. За елементи с висока товароносимост КРАЗ = 20 ... 30.

· Имунитет към статичен режим характеризира с напрежение Upst. ĸᴏᴛᴏᴩᴏᴇ нарича статично имунитет шум. Това е максимално напрежение на входа на статично смущения, в които няма промяна настъпва дори изходни нива на логика елемент.

· Консумираната мощност от захранването IC. Ако тази сила е различна за двете логически състояния, те често се посочва средният разход на енергия за тези държави.

· Праговите напрежения въвеждане на високи и ниски нива и Uvh.1porog Uvh.0porog На. съответстваща промяна в състоянието на логиката елемент.

· Напрежение на изхода на високи и ниски нива и Uvyh1 Uvyh0.

Използва се и други параметри.

Особености на различните логически елементи логиката. За дадена серия от чипове се характеризира с използването на стандартен електронен монтаж - основна логика елемент. Този елемент е основа за изграждане на широка гама от цифрови електронни продукти.

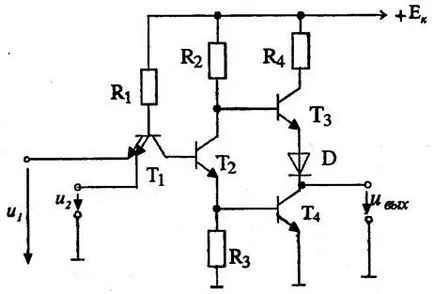

· Членът база включва TTL mnogoemitterny транзистор, който изпълнява логическа операция, и комплекс инвертор (фиг. 15.9).

Фиг. 15.9. TTL Базовата член

Ако един или двата входа едновременно хранени с ниско ниво на напрежение, транзистор mnogoemittterny е в състояние на насищане, и Т2 транзистор е затворен и поради това затворен и Т4 транзистор. т. е. на изхода е високо ниво на напрежение. В случаите, когато двата входа едновременно действащи ниво високо напрежение, Т2 транзистор се отваря и влиза в режим на насищане, което води до откриването и насищане на транзистора Т4 и Т3 транзистор е заключена. ᴛ.ᴇ. изпълнява функция NAND. За да се увеличи ефективността на елементи, използвани TTL транзистори с Schottky диоди или транзистори.

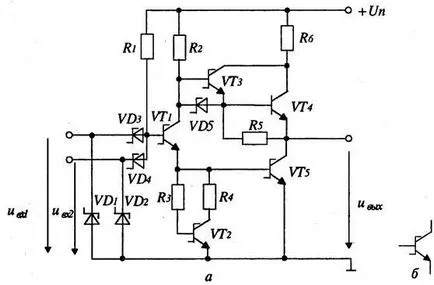

· Основния ключ STTL (на К555 серия например). Като база К555 серия елемент чипове използват елемент

И-НЕ (фиг. 15.10, а), и фиг. 15.10, б показва графично представяне на Шотки транзистор.

Фиг. 15.10. Логически елемент STTL

Транзистор VT4 - конвенционален биполярен транзистор.

· Захранващо напрежение от 5 V;

· Изходно напрежение ниско ниво на не повече от 0.4 V;

· Високо ниво на изходното напрежение не е по-малко от 2.5 V;

· Имунитет - не по-малко от 0.3 V;

· Средното време за забавяне на разпространението на 20 НЧ сигнал;

· Максималната работна честота 25 MHz.

Характеристики на други логики. Основата се основава логика елемент е ECL ток прекъсвач, чиято схема на токовите вериги е подобен на диференциален усилвател. Чипът се захранва ECL отрицателно напрежение (-4 V за K1500 серия). Транзистори на този чип не са в режим на насищане, което е една от причините за ECL клетки с висока скорост.

ключове чипове азот и фосфор -MOP -MOP се използват съответно за транзистори MOS с п-канал и динамично натоварване и MOS транзистори с р-канал. За да се премахне консумацията на логически елемент, използван в статично състояние допълнителни MOS-логически елементи (CVR или CMOS логика).

Логически базирани на полупроводникови GaAs галиев арсенид има най-високата скорост, която е следствие на мобилността на високо електрон (3 ... 6 пъти по-голяма в сравнение със силикон). Чипове на базата на GaAs могат да работят на честоти от 10 GHz.

Логическите устройства са разделени в два класа: комбинаторни и последователни.

Устройството се нарича Raman, ако нейните изходни сигнали в даден момент са еднозначно определени от входните сигнали, които се провеждат в даден момент.

В противен случай, устройството се нарича последователно или държавна машина (цифрова автоматична, автоматична с памет). В последователни устройства задължително елементи памет. Изходните сигнали от последователни устройства се определят не само сигнали на разположение на входовете в даден момент, но също и състоянието на елементите памет. Τᴀᴋᴎᴍ ᴏϬᴩᴀᴈᴏᴍ, реакция на последователни устройства за определяне ?? ennye входни сигнали в зависимост от нивото на историята на неговата работа.

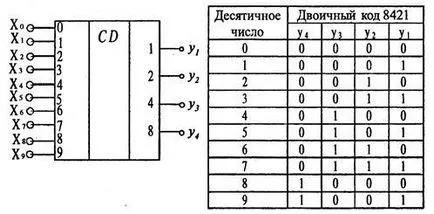

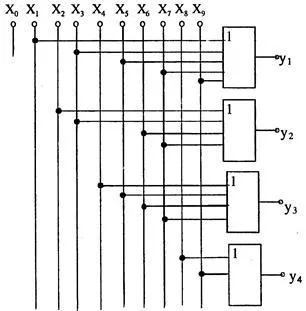

Encoder - ϶ᴛᴏ Раман устройство, което преобразува десетичното число на двоично число система, а всеки запис трябва да се зададе на десетични числа, както и набор от изходни логически сигнали съответства ?? ennomu определен двоичен код. Броят на входове и изходи в пълния кодер свързан връзка п = 2 m. където п - брой на входа, m - броят на изхода. Енкодер единица за превръщане на десет-цифров код (десетични числа от 0 до 9) в двоичен код. Схема на енкодер и кодовата таблица кореспонденция е показано на фиг. 11.1. С помощта на тази таблица за търсене, пишете на булеви изрази, включително логическа сума от тези входни променливи, които отговарят на единица продукция на променлива. По този начин, продукцията ще бъде логично y1''1 '' логика 'when''1 "ще бъде или на входа X1. или X2. или Х5. или X7. или X9. ᴛ.ᴇ. Y1 = X1 + X3 + X5 + X7 + X9.

Фиг. 16.1. Схемата на енкодер и кодовата таблица за справка

Ние представляваме на фиг. 16.2 верига като енкодер с помощта на или елементи.

Фиг. 16.2. Енкодер за ИЛИ порта

Ако на входа на слънце ?? EX - логическа единица, а след това ?? констатации бивш Sun също логическа единица, която съответства на броя 0 в така наречения обратен код (1111). В случай най-малко един входен отвор има логическа нула, тогава състоянието на изходния сигнал, определена от най-големия принос номер, който има логическа нула, и независимо от сигнали на входа, с по-малък номер.

Основната цел на енкодера - превръщане на изходния код в брой (например, броят чрез натискане на клавиатура).

Decoder нарича Раман устройство, което преобразува п-битовия двоичен код на логика сигнал се появява на изхода,

десетично число, което съответства на двоичен Cola. Броят на входове и изходи в така наречената пълна декодер, свързан връзка m = 2 п. където п - броят на влизанията и m - брой на изходите. Ако декодер използва непълен брой изходи, такъв декодер се нарича непълна. Така, например, декодер, с 4 входа и 16 изхода, ще бъде непълна, и ако изходът е само 10, а след това, че ще бъде в пълна степен.

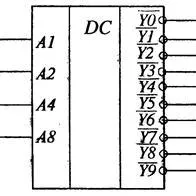

Нека например да декодер K555ID6 К555 серия (фиг. 16.3).

Фиг. 16.3. Шофиране декодер

Декодера - един от най-логически устройства са широко използвани. Той се използва за изграждане на многобройни комбинации от устройства. Декодери и енкодери са примери за прости кодове конвертор ?? ите.

Преобразователи кодове е устройство, проектирано да преобразува един код в друг, често те изпълняват кодове по поръчка на реализация. Транскодерите означени с X / Y.

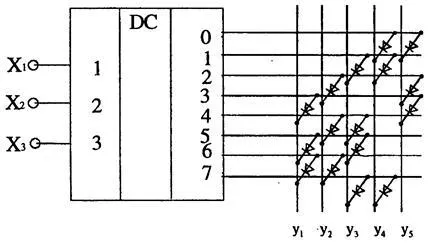

Помислете за изпълнението на определена част на инвертора за задвижване на примерен код три елемент за маса код кореспонденция пет елемент е показано на фиг. 16.4.

Фиг. 16.4. Кореспонденция маса на кодове за код конвертор

Тук N се обозначава с десетично число, съответстващо на двоичен код вход. Транскодерите създадена от декодер схема - енкодер.

Фиг. 16.5. Схема код конвертор

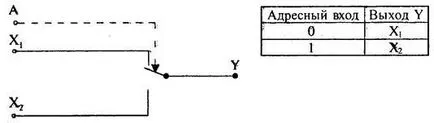

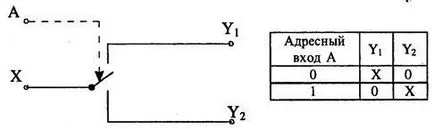

Разглеждане на действието на два входа мултиплексор (2 → 1), който е конвенционално изобразен като превключвател и състоянието му входове X1. Х2 и изход Y дадени в таблицата (фиг. 16.6).

Фиг. 16.6. два входа мултиплексор

Въз основа на таблицата, можете да напишете следното уравнение:

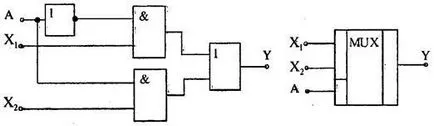

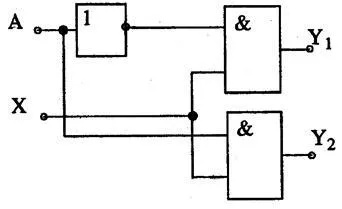

Фиг. 16.7 показва реализацията на такова устройство и условно графично нотация. В основата на тази схема е два елемента на съвпадение верига и които, когато логически level''1 '' на един от неговите входове се повтаря на изхода, който е в другия вход.

Фиг. 16.7. Изпълнение на два входа мултиплексор

една врата

Мултиплексори са общи логически устройства на базата на които се създават различни комбинаторни и последователни вериги. Мултиплексори могат да бъдат използвани в делител на честота, праговите устройства, срязване устройства за превръщане паралелно двоичен сериен и сътр.

Фиг. 16.8. Функционална схема на АЛ с два изхода

Разглеждане на действието на етапа на изместване с два изхода, който е конвенционално изобразени като превключвател, и вход състояние е показано в таблицата (фиг. 16.8). От тази таблица :, ᴛ.ᴇ. да реализира такава апаратура може да бъде, както е показано на фиг. 16.9.

Фиг. 16.9. Изпълнение на демултиплексиращото с два аута

една врата

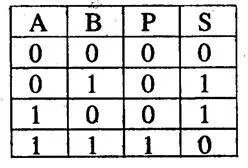

Adders - ϶ᴛᴏ комбинация устройство за комбиниране на номера. Помислете за добавяне на две единични-битови двоични числа, които представляват допълнение маса (истина масата), което ще се отрази на стойностите на входните числа А и В, стойността на сумиране резултат S и носят стойността в MSB P (фиг. 16.10). Операция изпълнява масата за истина, е описан от следните уравнения :.

Очевидно е, че по отношение на колона S се реализира логиката function''isklyuchayuschee ILI '', ᴛ.ᴇ. S = A Б.

Фиг. 16.10. истина таблица

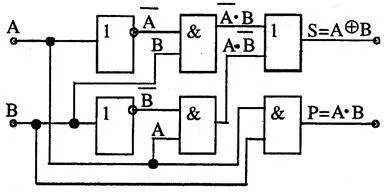

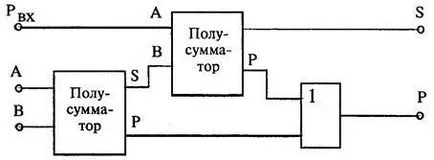

Апаратът, който реализира маса (фиг. 16,10), наречен половин разширител, и има логическа структура, показана на фиг. 16.11. Тъй като само половин ехидна има два входа, може да се използва за сумиране само най-маловажния бит.

Фиг. 16.11. Схемата на половин ехидна

В сумиране на двете мулти-битови числа за всеки бит (с изключение на младши) е изключително важно да се използва устройство, което има допълнителен вход за носене.

Фиг. 16.12. Схема пълен ехидна

Такова устройство (. Фигура 16.12) и се нарича пълен разширител и могат да бъдат представени като ?? IX комбинира две половин разширител (PJN - допълнителният вход пренос).

На суматора означен SM.

виж също

4-1. Концепцията за комбинация цифров чип устройство комбинация тип ниска степен на интеграция. Съгласно комбинаторни цифрово устройство (KTSU) се отнася до цифрово устройство, способно множество превръщане N на цифрови сигнали в М. [още].