въздействието на закъсненията

памет игра: внимание към закъсненията

Съвременните системи са много ненаситен в паметта - те трябва най-малко 512 MB, за предпочитане от 1 GB. Всичко е сложно, когато дойдеш в голям магазин за компютри - обикновено има голям избор на DDR400 модули от различни производители и в различни вариации. Разбира се, ние не се позовава на малки фирми с един вид памет на пазара. И така, какво памет да избера? Трябва ли да слушате това, което казва на продавача?

Всяко обсъждане на памет често се появява терминът "латентност / CAS латентност" или CL, за краткост. Но ние не трябва да забравяме и много други фактори, които се отразяват и на скоростта на паметта. В тази статия, ние внимателно ще обмисли тези фактори и да обясни смисъла на тези тайнствени фигури на модулите.

След това преминете към Целта на тази статия - за да се определи как системата ще работи с най-добрите, средното и най-лошите закъснения. Ние проведохме 19 отделни тестове на всички налични платформи (Athlon XP, Athlon 64, Athlon 64 FX, Pentium 4, Pentium 4 EE), за да хвърлят светлина върху този проблем.

Как SDRAM?

Съвременните модули памет предават пакети данни от 64 бита. DRAM чипове съдържат модули, които изпращат данни синхронно с часовник пулса и автобус обикновено се използва при повишена честота (DDR). Разликата между СПТ на гуми и DDR памет е, че данните за модула DDR предават по автобуса и на двата фронта на часовник пулса и СПТ - само един. Това е истинският тактова честота от DDR400 модули е 200 MHz, и ефективно - 400 MHz DDR.

Най-добрият показател за скоростта на модула с памет е един цикъл на времето, което е необходимо за приключване на един цикъл. Времето за цикъл от 10 НЧ памет означава, че можете да работите със скорост от 100 милиона цикъла в секунда, което означава, че чиповете могат да работят на 100 MHz. За да се постигне 133MHz, трябва 7,5 НЧ време на цикъла, и за 166 MHz - 6,0 NS.

Капацитетът на СПТ *

DDR трафик *

Как достъп до паметта

Паметта е организирана като матрица, където има редове (ред) и колони (колона). Капацитет чип зависи от броя на редовете и колоните. Ако няколко масиви са съчетани, те създават банка памет.

В съвременните компютри, командата скорост (команда процент), определен в BIOS - обикновено 1-2 цикъла. През това време, RAS се извършва след чипа памет на избор.

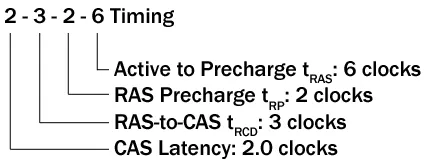

Контролерът избира памет активната линия. Но преди линията става активен, контролерът трябва да изчака 2-3 цикъла - tRCD (забавяне RAS-към-CAS). След това, командата за четене се изпраща, следван от латентността CAS. За DDR RAM памет, CAS латентност е 2, 2,5 или 3 цикъла. След този период приключи, данните ще пристигнат в DQ щифтове. След получаване на данни, контролерът трябва да деактивира ред, който се провежда по време на Trp (RAS време предналягане).

Има още едно техническо ограничение - Trás (активна до предналягане забавяне). Този минимален брой цикли по време на който на реда трябва да бъдат активни, преди да го отново ще бъде деактивиран. Обикновено Trás е 5-8 бара.

По-долу, ние имаме памет забавяне, в зависимост от тяхното значение: