Добив три изходни състояния

Чипове с три изходни състояния се появиха с развитието на информационните технологии. ИС се използват с три изходни състояния да се запечата каналите за предаване на информация, където информацията може да се предава и в двете посоки, както и за работата на няколко елемента от общото натоварване, за да се намали консумацията на енергия от източника на захранване.

Интегрирана изход верига може да има високо ниво U 1. U 0. Ниско ниво и третата OFF състояние, което се нарича висок импеданс или висок импеданс състояние. (Импеданс - комплекс импеданс.)

Една трета или Z-нарича състояние на забрана на информация рецепция, с което продукцията на NAND порта съпротивление отива до безкрайност и изходен ток - нула.

управление на чип е организирана по такъв начин, че във всеки един момент, всички чипове, с изключение на един, са по-високо съпротивление sostoyanii.Takim начин. в състояние да намали количеството на информационни магистрали. Според една обща шина може да предава информация по различни начини от няколко източника.

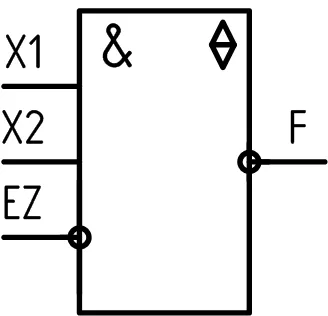

Фигурата показва 4.2 ASB логически NAND с Z-състояние.

Превод PE в трета държава играе активна сигнал с високо ниво на входа на EZ.

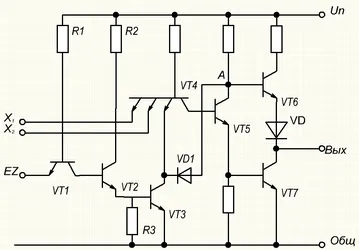

Фигура 4.3 е електрически схематична диаграма на логика И-НЕ елемент с Z-състояние.

Структурата на верига устройства включва:

· VT1 - ключът към ON, използвани за контрол на EZ Channel.

· VT2 - емитерен повторител. Той намалява тока през колектора VT1.

· R3 текущата ограничаване резистор.

· VT3 - ключ MA, управляван превключвател mnogoemitternogo транзистор VT4.

· VT4 -mnogoemitterny транзистор, който изпълнява логика функция.

· Други елементи - както в стандартен TTL елемент.

Помислете за функционирането на веригата на различни нива на EZ на входящия сигнал.

1. Когато EZ = 0 верига да работи като обикновено И порта. Текущи потоци от източника на звук VT1, VT2 е затворен, VT3 е затворен, VD1 затворен. VD1 е затворен, тъй като неговата основа (катод) е изключен от 0V). EZ канал не се отразява на работата на елемент, елементът изпълнява функцията 2И-НЕ.

2. Когато EZ = 1 VT1 транзистор работи в обратен режим. Текущи потоци от колектора VT1, VT2 и VT3 са отворени. На изхода на наситен образува VT3 0 и VD1 диод отваря.

В точка А е избран потенциал Ua = UKE.VT3 + UVD

0,9V. този капацитет е недостатъчен, за да се отвори и VT6 диод VD2 транзистор независимо от стойностите на входните сигнали.

Тъй VT3 се отваря, настоящите потоци през него от емитера VT4. Ето защо, ток колекционер на VT4 и не предполага VT5 транзистор е затворена. Също затворен транзистор VT7. Двете изходните транзистори са затворени (VT6 и VT7) и изход елемент е в Z-състояние.

Таблица 4.1 показва принципа на елементите на логически показани на Фигура 4.3.

Таблица 4.1 - Работна NAND порта с три изходни състояния

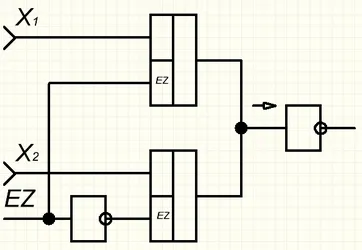

Фигура 4.4 показва пример на логически елементи с Z - състояние на общото натоварване.

Когато EZ е 1, елемент DD1 изход е в трета държава (офлайн). Element DD2 активиран и сигналите, изпратени от входната x2 на товара (LE HE).

Когато се работи по обща шина няколко елемента, само един е в експлоатация, а другите са с увреждания.

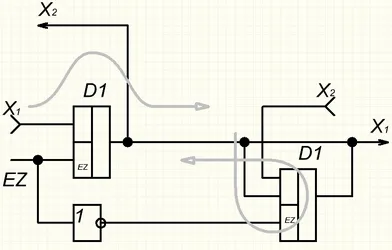

Фигура 4.5 показва, организацията на двупосочен пренос на данни.

Ако EZ = 0, тогава изхода е DD1 Z - състояние (затворен). Един изход елемент DD2 отворен, така че сигналът входа и на изхода се предава X2 Y2.

EZ = 1, DD2 изход е изключен и изходния елемент DD1 е свързан към линията, и се предава от X1 на входния сигнал на изхода U1. Тази схема е контролер на шината. Веригата изпълнява функцията на управление за предаване на информация от едно активно устройство за един или повече приемници.