схема схема

силова верига верига на биполярни транзистори

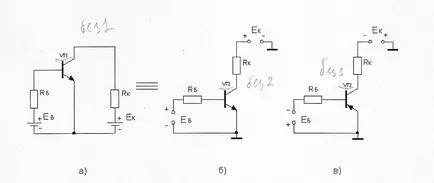

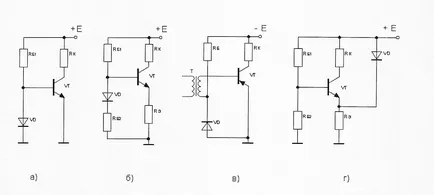

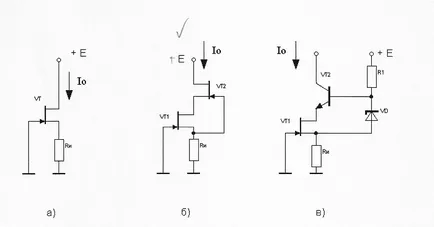

Фигура 1. статуси биполярен транзистор пристрастия напрежения:

а) N-р-п транзистор

б) различен вид на графично представяне

в) за р-п-р транзистор

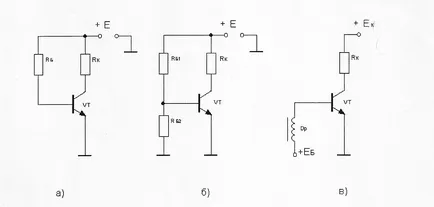

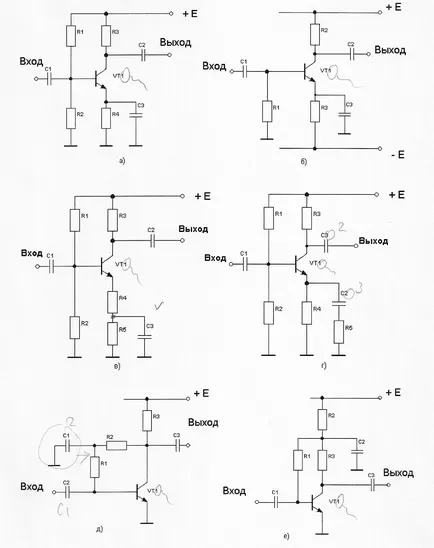

Фигура 2. Схема с фиксиран компенсира

а) с база фиксиран ток през Rb

б) постоянно напрежение на базата на

в) също с педала на газта в основната верига

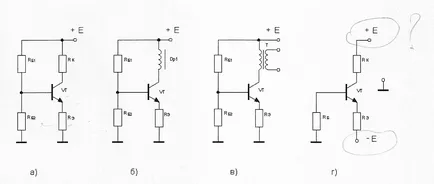

Фигура 3. Схема на биполярни транзистори с автоматично компенсира (емитер стабилизиране):

б) с газта като товар колектор

в) в етапа на трансформатор

ж) биполярно мощност

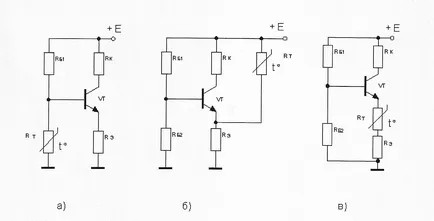

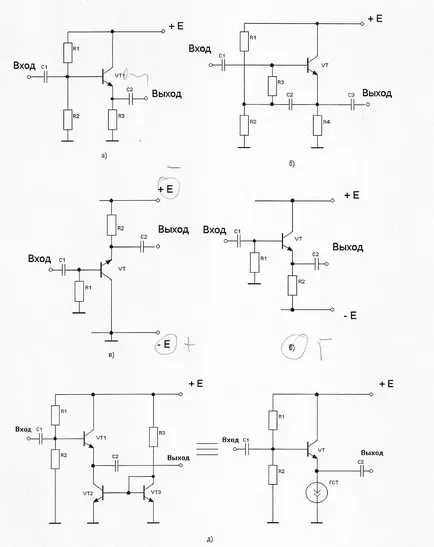

Фигура 4. Схема мощност биполярни транзистори с автоматично компенсира (колектор стабилизиране)

а) главната управляваща схема

б) като се използва филтър

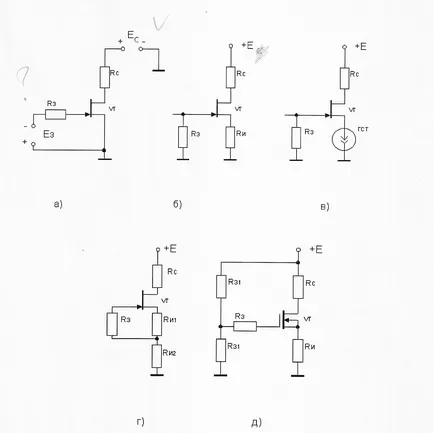

Фигура 5. Температура точка Схема за компенсиране почивка:

а), б) резистор с отрицателен температурен коефициент

в) резистор с положителен температурен коефициент

Фигура 6. Температура точка компенсация на почивка:

а) превключване диод верига база делител

б) превключване диод делител верига база в РС присъствие

в) в схема с входа на трансформатора

д) включване на диода във веригата за обратна връзка DC

на схема на полеви транзистори:

Фигура 7. FET на пристрастие напрежение:

а) с постоянно напрежение порта-източник

б), в) с автоматично превключване във веригата на източник

ж) с автоматично компенсира и частична смяна на веригата на източник

г) делител верига на портата

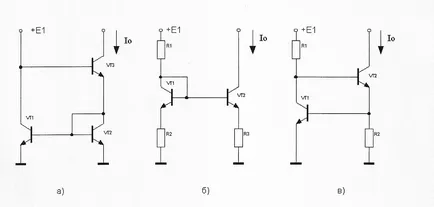

Фигура 8. Съединение транзистори:

а) Схематично Darlington

б) веригата Norton

в) транзистор поле ефект

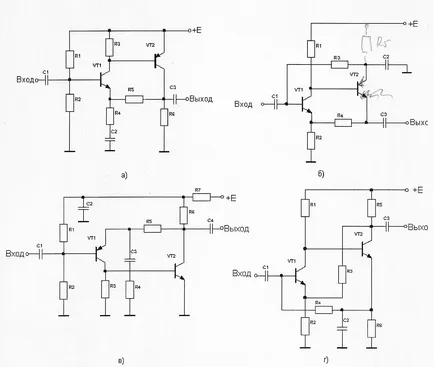

постоянен ток генератори (GTS)

Фигура 9. изпълнения на настоящите огледало вериги:

б) текущи контролирано резистори в емитер верига

в) по време на енергия с ниско напрежение

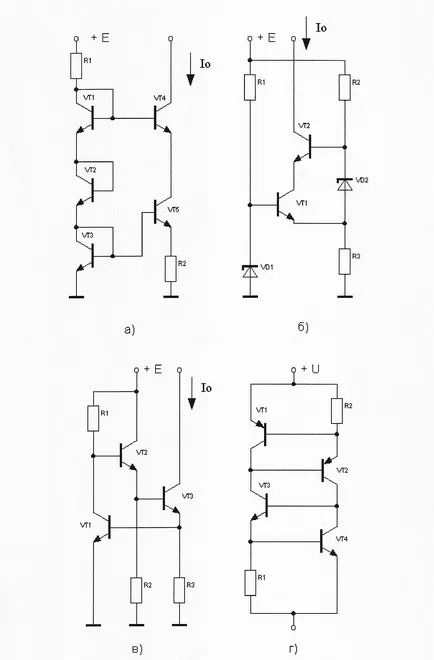

Фигура 10. GST с повишен изходен импеданс.

а) GTS разположени GTS

б) съединение транзистори MA-ON

в) за ток 3 mA

ж) dvuhvyvodnoy GTS (насрещни схеми включват две GTS [вж. фиг. 9 (в)])

стабилна текущата генератори FET

Фигура 11. GST FET:

а) най-простата схема

б) с повишен изходен импеданс

в) композитен GTS OI-ON с повишено напрежение

Фигура 13. позоваването на напрежение:

а) с намалена мощност съпротивление

б) mnogoemitternom транзистор

в) използване на база-емитер напрежение

г), д) контролирана стабилно напрежение, то с намалена мощност съпротивление, поради ООС VT1

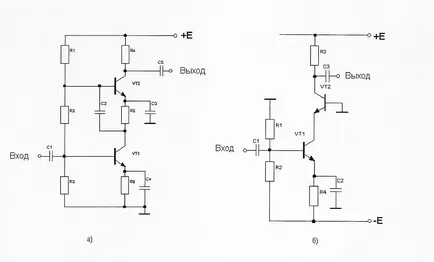

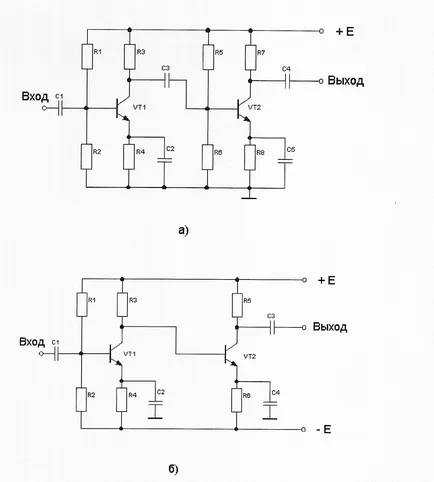

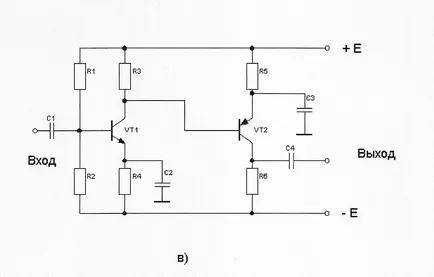

Фигура 14. усилвател каскади с ЕО:

а) и б) с емитер стабилизиране, без ОС сигнал

в) и г) с емитер стабилизиране и операционната система на сигнала

г), д) стабилизиране на колектора

Фигура 14. Етапите на амплификация с OK:

а) схема за каноничността

б) с високо входно съпротивление, не подминава разделител

в) и г) с биполярни мощност транзистори с различна проводимост и

г) текущата огледало като постоянен ток генератор

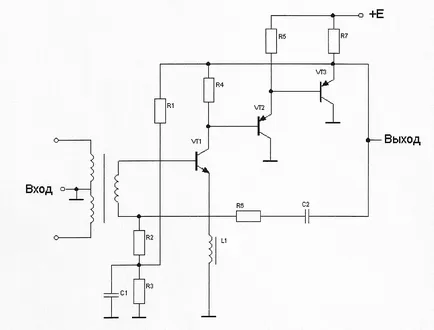

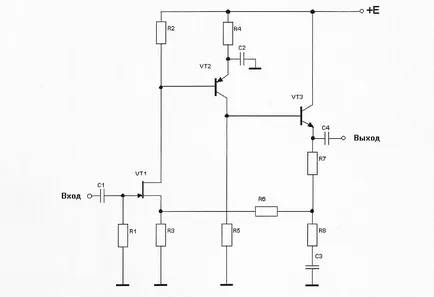

Фигура 16. усилвател съгласно схемата на MA-УО:

а), б), в) на комплементарната BT

г) по същата проводимост безжичният терминал

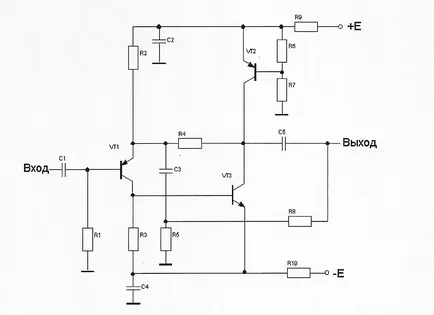

Фигура 20. Усилвателят два етапа с динамично натоварване.

Фигура 21. Усилвателят два етапа с диференциален вход съвпадение трансформатор и краен стадий на Darlington.

Фигура 22. Усилватели с последователни хранене.

Фигура 23. мощност за неутрализиране на входния капацитет.

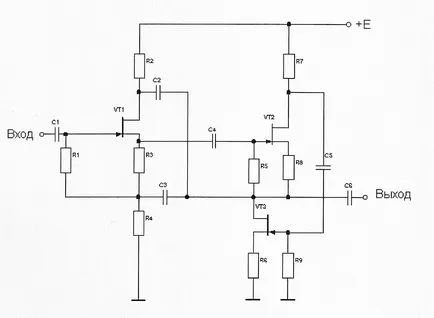

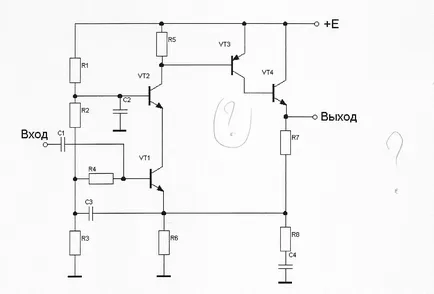

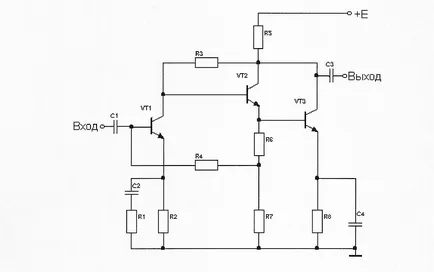

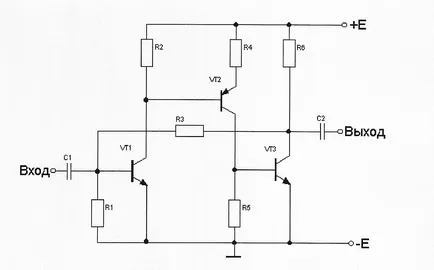

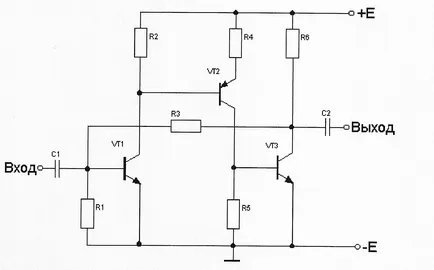

Фигура 24. двустепенно усилвател MA-УО

а) капацитивно свързва

б) с галванично свързване

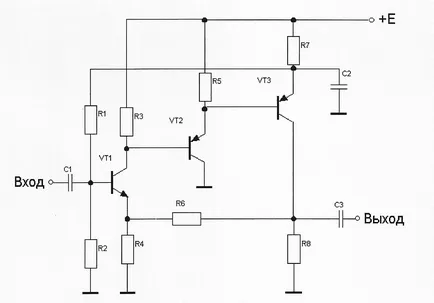

Фигура 24. двустепенно усилвател MA-УО

в) транзистори с различна проводимост

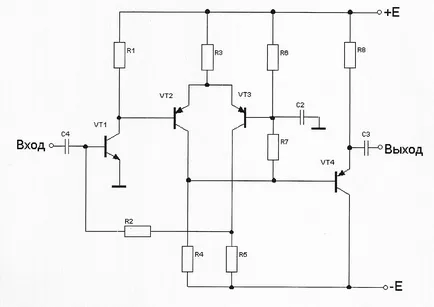

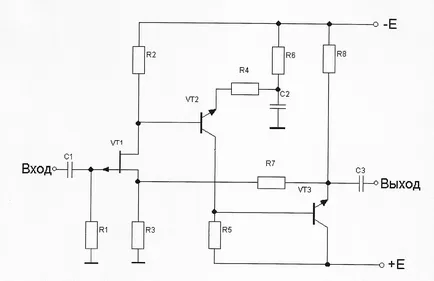

Фигура 25. усилватели тристепенни:

а) усилватели със структура, близка до ориза. 14 (д)

б) усилвател на мощност със сериен

Фигура 26. FET на усилвател на входа

Фигура 27. Мощност на базата cascode верига с високо входно съпротивление и Norton структура.

Фигура 28. Електрически преминава OS

Фигура 29. Мощност на широката операционната система.

Фигура 30. усилвател с диференциално етап.

Фигура 31. FET усилвателя и общото операционната система.

Фигура 32. Усилвателят с обща OS

Фигура 33. Усилвателят с обща OS