микроархитектура процесори

Начало »PC части» CPU микроархитектура

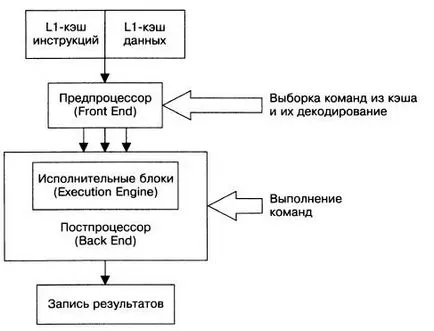

Преди да се пристъпи към разглеждането на истинските процесорни архитектури, евентуално движение напомня принципи на процесори на базата на проста структурна схема на хипотетично естество или "класически" процесор. Във всеки процесор на базата на архитектурата е по-конструктивни елементи: кеш инструкция и предпроцесорни за данни (Front End) и пост-процесор, наричан още блок за изпълнение на инструкции (Изпълнение на двигателя).

Процес данни се състоят от няколко типични стъпки. Първо на всички инструкции и данни са взети от L1 кеш (който е разделен на по-с инструкцията кеш и кеш за данни). Тази процедура се нарича проба. Тогава ти се закълна-кеша инструкции се декодират в разбираем за даден процесор примитиви (машинни инструкции). Това се нарича декодиране. На следващо място, се извършват декодирани инструкции, за да изпълнителните процесорни единици, и резултатът се записва в паметта.

вземане на проби обработва инструкции от кеш, декодиране и тяхното популяризиране на допълнително блокове е-извършвани в Препроцесорът, и изпълнението на процеса на декодирана инструкция - в постпроцесор. По този начин, дори и в най-простия случай на про-команда се извършва най-малко четири стъпки на обработка:

1. Пробата на кеш;

4. Запишете резултатите.

Тези стъпки се наричат тръбопроводите команди за обработка. В нашия случай, това е четири етапа тръбопровод. Важно е, че всяка от тези стъпки на екипа трябва да се проведе точно един такт. Съответно, за сто-поточна етап четири да изпълнява една команда се дава точно четири удара.

структурен оформление конвейер на "класическия" процесор

Разбира се, ние счита процесор е до известна степен хипотетична кал. В реални процесори инструкция тръбопровод обработка може да е по-сложна и включва повече стъпки. Въпреки това, самата структура на идеология на процесора остава непроменен. Причината за увеличаване на дължината на конвейера е, че много отбори са доста сложни и не може да се направи в един цикъл часовник, особено при високи честоти. Ето защо, всеки от четирите етапа на обработка на инструкции (донесе, декодиране, изпълнява, пиша) може да се състои от няколко етапа в тръбопроводите. Правилно, но дължината на конвейера е един от най-важните характеристики на всеки процесор.

В случая с "класически" метод за вземане на проби хипотетичен процес на изпълнение процесор с кодово настроен започва с инструкции и данни от L1 кеш. Въпреки това, с цел да се инструктаж и данни от кеша хит в това, те трябва да се заредят предварително съдържанието на паметта. Този процес се нарича предварително извличане на данни и инструкции от основната памет.

В съответствие със схемата на "класическата" процесор изпълнява процесуален кодекс процесор започва с инструкции за вземане на проби в x86 формат и данни от кеша L1. инструкции x86, са с различна дължина, а дължината на информацията за обучение се съхранява в специални полета в инструкциите за L1 кеш. Зареждане инструкции с различна дължина на x86 случва L1 кеш блокове на определена дължина, от което допълнително разграничени инструкции, които се подлагат на декодиране.

Когато се среща в поток бранш инструкция или преходи, вземане на проби блок на опашката-ТА инструкция се произвежда с помощта на механизъм клон прогноза.

Всеки процесор в крайна сметка трябва да бъдат конструирани така, че минималното време за извършване на максимален брой инструкции. Това е броят на изпълнените инструкции за единица време и определя производителността на процесора.

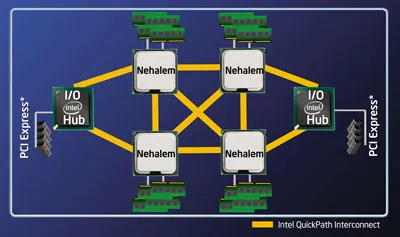

Има две коренно различни подходи за подобряване на производител-ност процесор (без да броим, разбира се, да се увеличи честотата на часовника). Са първите Второто е, че чрез намаляване на дължината на конвейера, за да се увеличи броят на единици за изпълнение. По този начин, по същество изпълнява множество къси паралелни транспортьори. В този случай, постпроцесор работи по класическата схема: извлича команди, да ги декодира и Изпращане на-а-Бу на няколко единици за изпълнение. Такъв подход позволява да се реализира напълно паралелизъм с инструкции-високо ниво (Инструкция ниво паралелизъм, ПИК), когато множество инструкции се изпълняват едновременно в различни изпълнителни процесори ING блокове. Важно е, че броят на етапа на тръбопроводите в постпроцесор (изпълнителния механизъм) е малък, така че твърденията се изпълняват за малък брой цикли.

За изпълнение на паралелизъм на ниво инструкция изисква след Payuschie до единици за изпълнение може да изпълнява команди паралелно. Въпреки това, ако, например, да извърши следните инструкции, за Tre buet знаят резултата от предишната инструкция (взаимозависими инструкции) на, в този случай, паралелно изпълнение не е възможно. Ето защо, предпроцесорни първо проверява взаимозависимост екипи и Пренареждане Chiva-те не са в реда получили (в ред), и така че те да могат да се изпълняват паралелно. В последния етап от инструкции за газопроводи RDS-ivayutsya в оригиналния ред.

Кратко тръбопровод, тъй като, наистина, и дълъг, има свои собствени силни и слаби страни Stora нас. Най-голям е броят на етапа, в който конвейера е разделена, минималния размер на работа се извършва във всеки етап и затова е необходимо по-малко време за завършване на този етап команда. Предвид факта, че всяка стъпка се извършва в един цикъл на обучение, дълги конвейери дават възможност да се увеличи честотата на часовника на процесора, което е невъзможно в случай на съвместно supershort транспортьори.

С кратко тръбопровод на всеки етап от процесора може да се справи с болката, сумата на шията на работа, но за преминаване инструкции през всеки етап на тръбопровода е необходимо повече време, което ограничава увеличаването на скоростта на процесора. В този случай, увеличаване на броя на изпълняваните инструкции за единица време, се постига чрез parallelizing инструктаж и се запълва-vanija изпълнителен процесорни единици.