Lab енкодер

учене схема на цифрови кодиращи устройства.

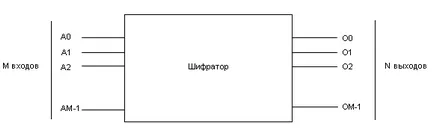

Encoder или програмист (енкодер) обикновено се отнася до устройство, което преобразува едноместно позиционен код, получена от клавиатурата, в който всеки вид двоичен код. Класически енкодер има M входове и nExiting, и при прилагане на активен сигнал към един вход (необходимо за един и не повече от) изхода е двоичен паралелно или успоредно на код, посочващ броя на възбуденото входа.

Фиг. Общата схема на енкодер

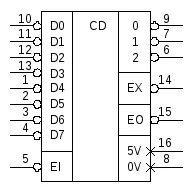

Ако енкодерът е оформен като един чип, е показано на диаграмата, както следва:

Приоритетни енкодери изпълняват по-сложни операции. Когато компютрите и други устройства често решава проблема за определяне на приоритет на заявителя за използването на даден ресурс. Няколко конкуренти проявяват своите заявки за услуги, които не могат да бъдат изпълнени едновременно. За да изберете този, който се дава право на приоритетните услуги. Най-простият вариант на решение на този проблем - задаване на всеки заявки източник втренчено втори приоритет. Например, група от осем zaprosovR7-R0 (angl.request Rot) е оформен така, че най-висок приоритет е nomersem източник и допълнително предимство намалява от стайна до стайна. Най-младият приоритет при нулево източник - това ще бъде връчен само с най-наличие на всички останали искания. Ако има няколко за просо, искания услуги с най-голям брой.

Приоритет енкодер генерира изход двоично число starshegozaprosa.

Лесно е да се види, че ако има само един вход развълнуван приоритет енкодер-ТА работи по същия начин като двоичен. Затова елементи в серия двоичен енкодер като отделен елемент, могат да бъдат пропуснати. При повторно натискане на делото му - специален случай на приоритет енкодер.

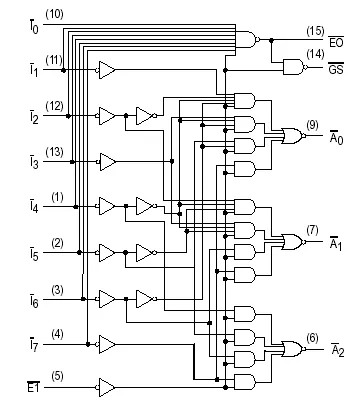

В индустриалната серия елементи са приоритет енкодер за осем и десет-цифрен думи. Функциониране на техните дисплеи в таблицата.

Таблица напълно характеризира приоритет работа енкодер за всички възможни комбинации на сигнала на: EI- сигнала за разрешаване на енкодер; E0 - сигнал, генериран на изхода на кодера, когато не са направени заявки за своя принос за разрешение на следващия (младши) в ескалацията на енкодери шифър-измерение цветно легло; G - сигнал маркировка присъствието на входа на референтния код заявка Rhatore; R7-R0 - искания за входове енкодер; а2-A0 - стойностите на празнина-ING изхода двоичен код формиране старшият по заявка номер. Всички тези сигнали са генерирани когато (е позволено работа shifrato-ра) usloviiEI = 1. PriEI = 0, независимо от щатите всички входове поиска изходните сигнали на енкодер става нула.

Капацитет приоритет измерение енкодер

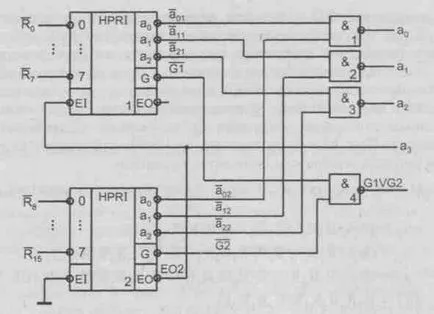

Символ приоритет енкодер е показана на фиг. където броят на искания вход капацитет е показана два пъти (8 до 16). В същото време той показва енкодери с обърнати входове и изходи, както е характерно за по-голямата част от елементите на серия.

Encoder 2 - старши в приоритет на работата си винаги е активирана доставка нула на входа EI2. Ако vhodahR8. R15est поне една молба, времевите решения, за да работят по-младото енкодер № 1 (E02 = 1). 1 енкодер изходи са пасивни, т.е.. Д. Имат една стойност. Така И-НЕ елементи с индекс зададена 1, 2, 3 служи като инвертори за AI2 на сигнала (I = 0, 1, 2). Следователно, A0 изходите, А1, А2 верига обикновено се образуват сигнали от нула до седем над зависимост от броя на най искане енкодер 2, които заедно с изходния блок на П02 дава номера 8-15.

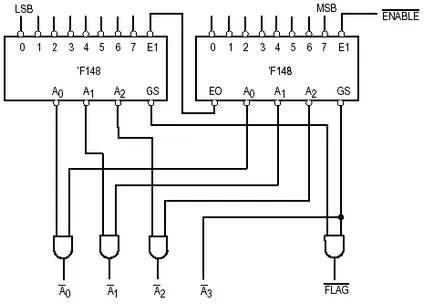

Фиг. Схема капацитет приоритет измерение енкодер

Ако енкодер 2 искания вход Не, това дава възможност на млади, разработване на сигнала E02 = 0, и предизвиква неговата продукция a0, a1, A2B пасивна една държава. Сега изходите и в общата схема предава Inver Тед ценности vyhodova01, a11, a21 младши енкодер, който snulem заедно в А3 изпускателния кореспондира с цифрите от нула до седем.

По този начин, веригата е конструиран с 16 входни искания, където R15 има най-висока влизане приоритет. Добив елемент 4 получава една стойност, когато по-lichii поне едно искане в някоя от енкодери, и може да се използва като заявка за прекъсване сигнал на процесора, последвано от номера на високата заявка процесора.

Ако всяка цифра от десетично число в двоичен представят еквивалентен, резултатите, получени под формата на код, наречен BCD. Тъй десетичната може да бъде равно на 9, четирите бита са необходими за кодиране на всеки razryd (двоичен код 1001 е равно на 9).

08 юли 4 (десетичен код)

1000 0111 0100 (BCD)

Така BCD представлява всяка цифра от десетична номер четири битова двоична цифра. Тя използва само номера от 0000 до 1001. BCD код не използва номера 1010, 1011, 1100, 1101, 1110 и 1111. С други думи, които се използват само 10 от 16 възможни групи от по четири-двоичен код. Ако изведнъж колата, работа с BCD, по някакъв начин да получи един от тези "забранени" числа, обикновено е съобщение за грешка.

На инструкциите на учителя изпълнява реализации между двоична, десетична, осмична и шестнадесетична номера.

Запишете логическите изрази, които описват работата на сглобени веригата.

Начертайте схема на диодна енкодер за вашата истина маса.

Разбиране на интегрална схема приоритет енкодер K555IV1 (74148):

Разберете верига 16-вход приоритет енкодер, състоящ се от два чипа 74148 (диаграма, взети от документацията firmyMOTOROLA 74F148):

Какво е кодът на BCD и неговата област на приложение?

Грей код, неговите функции и обхват?

Каква е приоритет енкодер?

Каква е точка С е на изхода на вашия кръг?