Двустепенна T-тригер - studopediya

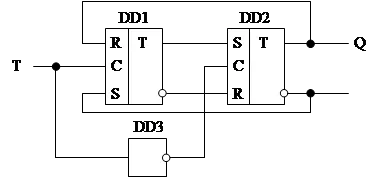

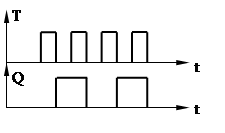

В спусъка два етапа, съдържащ две серии включва капаче с обратни връзки, "новите" информацията се съхранява в първия тригер при поддържане на "стари" информация във втория. Когато "нов" информацията се съхранява, и активен сигнал се отделя от входа TS изтрива "стари" информация и презаписване на "нов" информацията на втория спусъка. Схема двустепенна T-тригер, построена на два синхронни RS-джапанки и неговото функциониране времето диаграма е показано на фиг. 5.9.

Фиг. 5.9. Схема (а) и времедиаграма на (б) на два етапа T-тригер

Двуетапна T тригер се състои от две джапанки - главен и подчинен DD1 DD2. За да се премахне поколение режим верига часовник входове на джапанки включени чрез DD3 инвертор, т.е. синхронизация се получава обърнати логически нива. Обратни с директен достъп до входа DD2 R DD1 и DD2 обърнат изход S DD1 да създават сигнали съвпадение алгоритъм работи T-тригер. Имайте предвид, че на изхода от два етапа T-тригер появява след отстраняване на активно входния сигнал Т, когато информацията се презаписва от първия тригер във втория. Това гарантира нормална работа (без генериране на импулс) в схема с обратна връзка.

За да се различава двустепенен спусъка с едностепенна, условно си графично изображение се поставя двойно писмо (TT).

5.6. двустепенна едновременно JK -trigger на

Отличителна черта на JK -triggera е, че тя е не е забранено комбинации от входни сигнали в входа на информация. JK -triggera работа описва преход таблица (Таблица 5.5), в която се счита за активен сигнал логическа 1. активни J входни спусъка сигнал превключва в състояние Q = 1, и К вход - при Q = 0.

Таблица преминава JK -triggera

Фиг. 5.10. Блок-схема JK -triggera

Както може да се види от диаграмата, входовете на елементи 3I DD3 или DD4 DD2 снабдени с изхода на спусъка сигнал логическа 0 и логическа единица. Следователно, входовете J и К могат да бъдат всички сигнали, но в S и R DD1 входове едновременно две активни сигнал не може да се достигне.

JK -trigger е универсална. Въз основа на това, можете да създадете всякакъв вид тригер схема. Фиг. 5.11 показва изпълнението на всички досега се смятаха за JK джапанки -triggere.

Фиг. 5.11. Изпълнение на тригери, основани на JK -triggera:

и - синхронен RS-FF; б - D-тригер; в - Т-тригер

В поредица от TTL JK -trigger прави на K155TV1 чип, CMOS серия - K561TV1 и K176TV1, това е всичко в един чип в серията. Това се дължи на ниското търсене за джапанки със статично контрол за използване в системи за автоматизация и дистанционно управление.