Комбинирани цифрови устройства

Raman цифрово устройство (KTSU) - е устройство, което подава в определен момент от време се определя еднозначно от входните сигнали. В KTSU използва не само отделят логически елементи прилагане елементарните булеви функции, но също така и комбинации от тях, обикновено интегрално оформени под формата на интегрални схеми. Входовете KTSU информация доставени логически сигнали и сигнали за управление, които определят реда на предаване на информационни сигнали на входа и на изхода на процеса на синхронизация. Типично широко използваната KTSU на практика включват: кодови преобразуватели, енкодери, декодери, мултиплексори, демултиплексори (селектори), цифрови компаратори, разширители, както и мулти-входни преобразуватели на типа и-ИЛИ-НЕ.

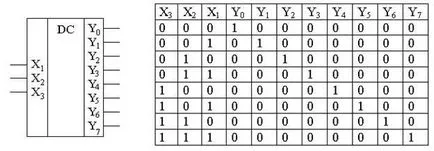

Най-декодер (декодер, окръг Колумбия), наречена KTSU който преобразува п-битов двоичен код в активен логично изходен сигнал, десетичното число, което съответства на двоичен код вход. Ако количеството на О 2 равна m = п. където п - брой входове, декодера се нарича пълна. Когато по-малко изходи декодер ще бъдат непълни. Фигура 7.20 показва символът на пълната декодер 3-8 и истина маса.

Този декодер е описан от следния набор от логически изрази:

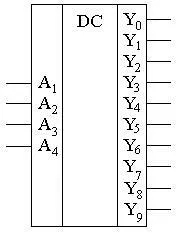

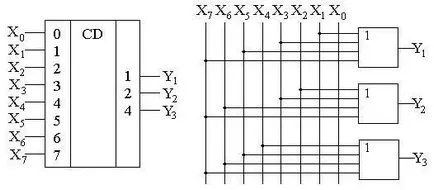

Encoder (програмист, CD) - това Раман устройство, което преобразува десетично число в двоичен. На ris.7.23 показан символ изпълнение енкодер и 8-3 (осем входа до изхода три) по базисни елементи.

Таблицата с истината за този енкодер е (Tab.7.1). Функционални уравнения са равни

От съотношението на броя на входовете и изходите М Н енкодери са пълни (m = 2 N) и непълна (т <2 n ). В приоритетных шифраторах выходной двоичный код соответствует наивысшему номеру входа, на который подан активный сигнал (независимо от наличия сигналов на других входах).

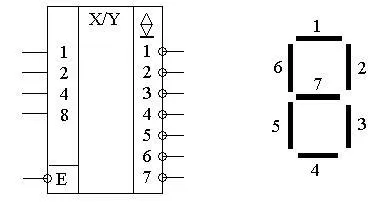

В цифровата техника, използвана различни видове кодове за обработка на информация и предаване (напред, назад, трети, BCD, сиво код, Hamming кодове и т.н.). Код преобразуване извършва на комбинаторни устройства на ниво хардуер - транскодерите. Тези устройства включват също множество преобразуватели бар графика контрол, матрица и седем дисплей сегмент. Избраните кодови преобразуватели чрез X / Y. код конвертор често се прилагат съгласно разпоредбите декодер схема - енкодер. Всеки тип датчик се характеризира със съответния истина масата. Специален случай на конвертори кодове са кодиращи и декодиращи. На ris.7.24 показва конвертор BCD до седем-сегмента код дисплей.

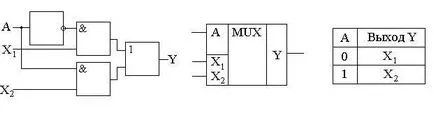

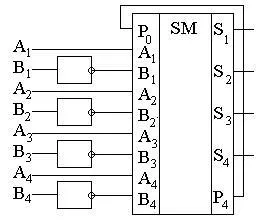

Мултиплексор - Раман устройство, способно да предава цифрова информация, получена при много входове към един изход в съответствие с предварително определен код за управляващите входове. В действителност, това успя ключ. Също така сред п брой управляващи входове и броя на информационните входове е валидна връзка m = 2 до п мултиплексор пълен и непълен m <2 n. Мультиплексоры обозначают MUX или MS. На рис.7.25 показана функциональная схема двухвходового мультиплексора, условное обозначение и таблица коммутации.

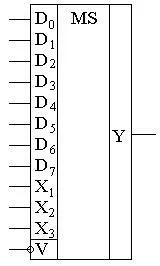

На ris.7.26 показано селектор-мултиплексор 8/1. В зависимост от комбинацията на управляващи сигнали x1x2x3 осигурява превключване на една от осем входни сигнали Di към изхода Y като V - резолюция, активно ниско. Функционално уравнение в писмена форма

Мултиплексори са общи логически устройства на базата на които се създават различни комбинаторни и последователни вериги. Те се използват в делител на честота, задейства устройства, преместващи регистъра, инвертори успоредно на сериен, изпълняват сложни логически функции.

Функционални уравнения, описващи работата му, както следва:

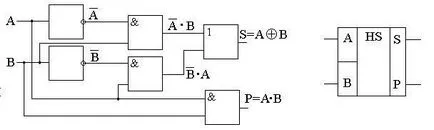

Adders - комбинация устройство пригоден да добавяне на номера. Таблицата с истината за добавянето на две единични номера А и Б ще

където S - стойността на сумата от P - прехвърляне на стойността в MSB. Операцията е описан от следните уравнения

Това може да се види, че сумата съответства на функцията логика "XOR» S = A ÅБ. устройство, което осъществява тази таблица нарича половин разширител и неговата структура е показана в ris.7.29.

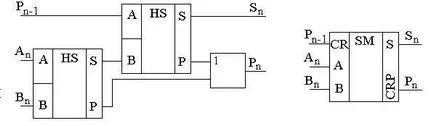

А един-битов пълен усойница се основава на две полу-усойница. Неговата структура и символ, показан на ris.7.30. За разлика от това, че има период на ехидна носене от LSB.

Таблицата с истината за суматора се изчислява по формулата

За да обобщим многобитови двоични числа разширители свързани последователно, както и прехвърлянето на производството в най-маловажният бит е свързан към общия проводник. Под формата на интегрални схеми са произведени един, два и четири битови разширители. С помощта на ехидна и изваждане може да произвежда двоични числа. В този случай, изваждане се заменя с добавяне на умаляемото с умалителят по два на

На ris.7.31 показано изваждащ базирани chetyrohrazryadnogo усойница. Броят е обърнат и се прибавя към и да прехвърли хранени логическа единица.